# **GR533x Hardware Design Guidelines**

Version: 1.1

Release Date: 2023-11-14

Shenzhen Goodix Technology Co., Ltd.

### Copyright © 2023 Shenzhen Goodix Technology Co., Ltd. All rights reserved.

Any excerption, backup, modification, translation, transmission or commercial use of this document or any portion of this document, in any form or by any means, without the prior written consent of Shenzhen Goodix Technology Co., Ltd. is prohibited.

#### **Trademarks and Permissions**

**GODIX** and other Goodix trademarks are trademarks of Shenzhen Goodix Technology Co., Ltd. All other trademarks and trade names mentioned in this document are the property of their respective holders.

#### Disclaimer

Information contained in this document is intended for your convenience only and is subject to change without prior notice. It is your responsibility to ensure its application complies with technical specifications.

Shenzhen Goodix Technology Co., Ltd. (hereafter referred to as "Goodix") makes no representation or guarantee for this information, express or implied, oral or written, statutory or otherwise, including but not limited to representation or guarantee for its application, quality, performance, merchantability or fitness for a particular purpose. Goodix shall assume no responsibility for this information and relevant consequences arising out of the use of such information.

Without written consent of Goodix, it is prohibited to use Goodix products as critical components in any life support system. Under the protection of Goodix intellectual property rights, no license may be transferred implicitly or by any other means.

#### Shenzhen Goodix Technology Co., Ltd.

Headquarters: Floor 12-13, Phase B, Tengfei Industrial Building, Futian Free Trade Zone, Shenzhen, China

TEL: +86-755-33338828 Zip Code: 518000

Website: www.goodix.com

## Preface

#### Purpose

This document presents the necessary circuit required for proper operation of GR533x Bluetooth System-on-Chips (SoCs). Recommended chip interfaces, peripherals, schematic diagram, and PCB layout guidelines of the GR533x SoC family are provided.

This *Hardware Design Guidelines* intends to help system designers build minimal Bluetooth Low Energy (Bluetooth LE) hardware circuits and develop Bluetooth products.

#### Audience

This document is intended for:

- Device user

- Developer

- Test engineer

- Technical support engineer

#### **Release Notes**

This document is the second release of *GR533x Hardware Design Guidelines*, corresponding to GR533x SoC series.

#### **Revision History**

| Version | Date       | Description                      |

|---------|------------|----------------------------------|

| 1.0     | 2023-10-18 | Initial release                  |

| 1.1     | 2023-11-14 | Updated the power supply scheme. |

## Contents

| Preface                               | I  |

|---------------------------------------|----|

| 1 Product Overview                    | 1  |

| 1.1 Features                          |    |

| 1.2 Block Diagram                     | 4  |

| 1.3 Applications                      | 5  |

| 2 Pinout                              | 6  |

| 2.1 QFN32                             | 6  |

| 2.2 QFN48                             |    |

| 2.3 Pin Properties                    |    |

| 2.3.1 PMU Pin Properties              |    |

| 2.3.2 I/O Pin Properties              |    |

| 3 Minimal Design for GR533x SoC       | 14 |

| 3.1 Schematic Design Guideline        |    |

| 3.1.1 Power Supply                    |    |

| 3.1.1.1 Introduction                  |    |

| 3.1.1.2 Power-on Sequence             |    |

| 3.1.1.3 I/O LDO                       |    |

| 3.1.1.4 Power Supply Scheme           |    |

| 3.1.2 Clock                           |    |

| 3.1.2.1 Introduction                  |    |

| 3.1.2.2 HFXO_32M                      | 22 |

| 3.1.2.3 LFXO_32K                      | 24 |

| 3.1.3 RF                              | 25 |

| 3.1.3.1 Introduction                  | 25 |

| 3.1.3.2 RF Scheme                     | 27 |

| 3.1.4 I/O Pins                        |    |

| 3.1.5 SWD Interfaces                  |    |

| 3.2 PCB Design and Layout Guideline   |    |

| 3.2.1 PCB Layer Stackup               |    |

| 3.2.2 Components Layout               |    |

| 3.2.3 Power Supply                    |    |

| 3.2.3.1 DC-DC Switching Regulator     |    |

| 3.2.3.2 RF Input Power Supply         |    |

| 3.2.4 Clock                           |    |

| 3.2.5 RF Port                         |    |

| 3.2.6 RSE Certificate Recommendations |    |

| 3.3 ESD Protection Design             |    |

| 3.3.1 System-level ESD Design         |    |

# G@DiX

| 3.3.1.1 ESD Schematic Design                                     |    |

|------------------------------------------------------------------|----|

| 3.3.1.2 PCB Layout Design                                        |    |

| 3.3.1.3 Product Structural Design                                |    |

| 3.3.2 ESD Considerations in Production, Transport, and Debugging | 40 |

| 3.4 Reference Design                                             |    |

| 4 FAQ                                                            |    |

| 4.1 Why Is the Power Consumption in GR533x Sleep Modes High?     |    |

| 4.2 Can the RF Matching Circuits Be Simplified or Removed?       | 42 |

| 5 Glossary                                                       | 44 |

| 6 Appendix: Assembly Guideline                                   | 46 |

| 6.1 Package Information                                          | 46 |

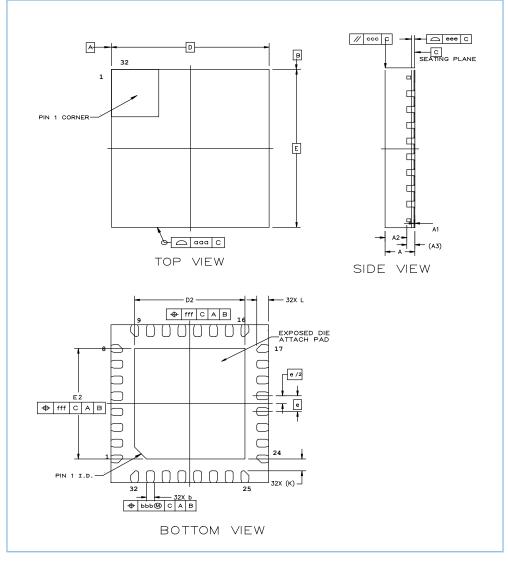

| 6.1.1 QFN32                                                      |    |

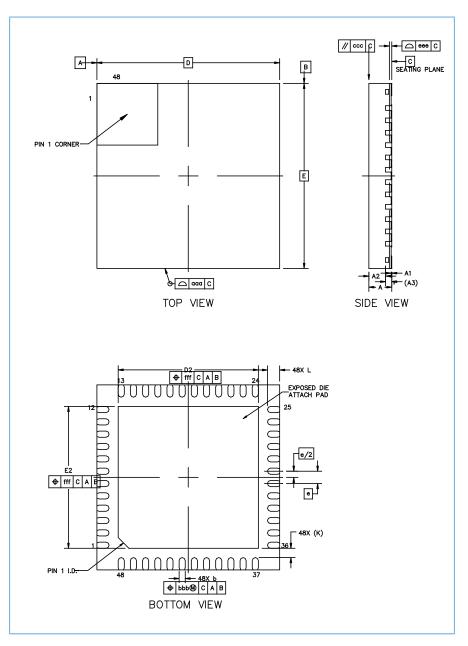

| 6.1.2 QFN48                                                      |    |

| 6.2 Board Mounting Guideline                                     |    |

| 6.2.1 Stencil Design for Perimeter Pads                          |    |

| 6.2.2 Via Types and Solder Voiding                               |    |

| 6.2.2.1 Stencil Thickness and Solder Paste                       |    |

| 6.2.2.2 PCB Materials                                            |    |

| 6.2.3 SMT Printing                                               | 53 |

| 6.3 SMT Reflow Process                                           | 53 |

| 6.4 Rework Guideline                                             |    |

| 6.4.1 Component Removal                                          | 56 |

| 6.4.2 Site Redress                                               | 56 |

| 6.4.3 Solder Paste Printing                                      | 57 |

| 6.4.4 Component Placement                                        |    |

| 6.4.5 Component Attachment                                       |    |

| 6.5 RoHS Compliant                                               |    |

| 6.6 SVHC Materials (REACH)                                       | 57 |

| 6.7 Halogen Free                                                 | 57 |

|                                                                  |    |

## **1** Product Overview

The Goodix GR533x series is a Bluetooth Low Energy (Bluetooth LE) 5.3 System-on-Chip (SoC), suitable for Internet of Thing (IoT) applications, supporting Bluetooth mesh networking protocols.

Based on Arm<sup>®</sup> Cortex<sup>®</sup>-M4F CPU core running at 64 MHz, the GR533x integrates a 2.4 GHz RF transceiver, Bluetooth LE 5.3 protocol stack, 512 KB on-chip Flash memory, 96 KB system SRAM, and a rich set of peripherals. It provides excellent RF performance, with a maximum of +15 dBm TX power, -99 dBm RX sensitivity and a maximum of 114 dB link budget in Bluetooth LE 1 Mbps mode.

With two main power supply schemes (DC-DC and system LDO), the GR533x offers flexible options to achieve a balance between low power consumption and economical BOM.

GR533x devices are offered in both QFN32 and QFN48 packages. The following table lists the detailed package configurations.

| Part Number              | GR5331AENI                              | GR5331CENI                              | GR5332AENE                              | GR5332CENE                              |

|--------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|

| CPU                      | Cortex <sup>®</sup> -M4F                | Cortex <sup>®</sup> -M4F                | Cortex <sup>®</sup> -M4F                | Cortex <sup>®</sup> -M4F                |

| RAM                      | 96 КВ                                   | 96 KB                                   | 96 КВ                                   | 96 КВ                                   |

| SiP Flash                | 512 KB                                  | 512 КВ                                  | 512 КВ                                  | 512 КВ                                  |

| TX power                 | Up to 6 dBm                             | Up to 6 dBm                             | Up to 15 dBm                            | Up to 15 dBm                            |

| RX sensitivity           | -97.5 dBm @ 1 Mpbs                      | -97.5 dBm @ 1 Mpbs                      | -99 dBm @ 1 Mpbs                        | -99 dBm @ 1 Mpbs                        |

| Consumption              | 3.8 mA TX @ 0 dBm<br>4.7 mA RX @ 1 Mbps | 3.8 mA TX @ 0 dBm<br>4.7 mA RX @ 1 Mbps | 5.9 mA TX @ 0 dBm<br>4.9 mA RX @ 1 Mbps | 5.9 mA TX @ 0 dBm<br>4.9 mA RX @ 1 Mbps |

| I/O number               | 16                                      | 32                                      | 16                                      | 32                                      |

| Operating<br>temperature | -40°C to 85°C                           | -40°C to 85°C                           | -40°C to 105°C                          | -40°C to 105°C                          |

| Package (mm)             | QFN32 (4 x 4 x 0.75)                    | QFN48 (6 x 6 x 0.75)                    | QFN32 (4 x 4 x 0.75)                    | QFN48 (6 x 6 x 0.75)                    |

Table 1-1 GR533x series

## 1.1 Features

- Bluetooth LE 5.3 transceiver

- Supported data rates: 1 Mbps, 2 Mbps, and Long Range (500 kbps, 125 kbps)

- TX power:

- Up to 6 dBm on GR5331

- Up to 15 dBm on GR5332

- RX sensitivity:

- -97.5 dBm @ 1 Mbps on GR5331

- -99 dBm @ 1 Mbps on GR5332

- Power consumption at 3.3 V VBAT input on GR5331:

- 3.8 mA TX current @ 0 dBm output power (DC-DC supply, 16 MHz system clock)

- 4.7 mA RX current @ 1 Mbps (DC-DC supply, 16 MHz system clock)

- Power consumption at 3.3 V VBAT input on GR5332:

- 5.9 mA TX current @ 0 dBm output power (DC-DC supply, 16 MHz system clock)

- 86.3 mA TX current @ 15 dBm output power (SYS\_LDO supply, 64 MHz system clock)

- 4.9 mA RX current @ 1 Mbps (DC-DC supply, 16 MHz system clock)

- Arm<sup>®</sup> Cortex<sup>®</sup>-M4F 32-bit micro-processor with floating point support:

- Up to 64 MHz clock frequency

- Built-in Memory Protection Unit (MPU) supporting eight programmable regions

- Hardware Floating Point Unit (FPU)

- Built-in Nested Vectored Interrupt Controller (NVIC)

- Non-maskable Interrupt (NMI) input

- Serial Wire Debug (SWD) with 16 breakpoints, two watchpoints, and a debug timestamp counter

- ° 32 μA/MHz CoreMark running from Flash @ 3.3 V, 64 MHz from HFRC

- On-chip memory

- 96 KB RAM data memory with retention capabilities

- 8 KB cache RAM instruction memory with retention capabilities

- ROM for boot and partial Bluetooth LE Protocol Stack code

- 512 KB internal Flash

- Digital peripherals

- 1 x general-purpose DMA engine with five channels and 16 handshaking interfaces

- Analog peripherals

- 1 x 13-bit Sense ADC with a sampling rate of 1 Msps, supporting up to eight external I/O channels and three internal signal channels

- Built-in die temperature and voltage sensors

- Low-power comparator, supporting wakeup from sleep mode

- Flexible serial peripherals with arbitrary mapping on all digital I/Os

- 2 x UART modules up to 2 Mbps with flow control and IrDA features

- 2 x I2C modules for peripheral communication, up to 1 MHz, operating as either Master or Slave

# GODiX

- 1 x 8-bit/16-bit/32-bit SPI master interface and 1 x SPI slave interface for host communication

- Security

- AES 128-bit security module (ECB, CBC)

- True random number generator (TRNG)

- I/O peripherals

- Up to 32 multiplexed I/O pins in total

- Up to 14 general-purpose I/O (GPIO) pins with configurable pull-up/pull-down resistors

- Up to eight always-on I/O (AON I/O) pins, supporting wakeup from sleep mode

- Up to 10 mixed signal I/O (MSIO) pins, configurable to be digital/analog signal interfaces

- Timers

- 2 x 32-bit general-purpose timers

- 1 x dual timer with two programmable 32-bit or 16-bit down counters

- 1 x sleep timer for waking the device up from sleep mode

- 2 x 3-channel PWMs with edge-aligned mode and center-aligned mode

- 1 x real-time counter

- Power management

- On-chip DC-DC/SYS\_LDO to provide RF analog voltage and supply CORE\_LDO

- On-chip I/O LDO to provide I/O voltage and supply external components

- Programmable thresholds for brownout detector (BOD)

- Supply voltage: 2.0 V–3.63 V

- I/O voltage: 1.8 V–3.6 V

- Low-power consumption

- Sleep mode: 2.6 μA (Typical) at 3.3 V VBAT input, with 48 KB SRAM retention on, wakeup sources from AON

I/Os, and LFXO\_32K running

- Ultra deep sleep mode: 1.9 μA (Typical), with no memory data in retention and wakeup sources from SLP Timer or AON I/Os

- OFF mode: 200 nA (Typical), with system in reset mode

- Operating temperature range

- GR5331: -40°C to 85°C

- GR5332: -40°C to 105°C

- Packages

- QFN32: 4.0 x 4.0 x 0.75 mm, 0.4 mm pitch

- QFN48: 6.0 x 6.0 x 0.75 mm, 0.4 mm pitch

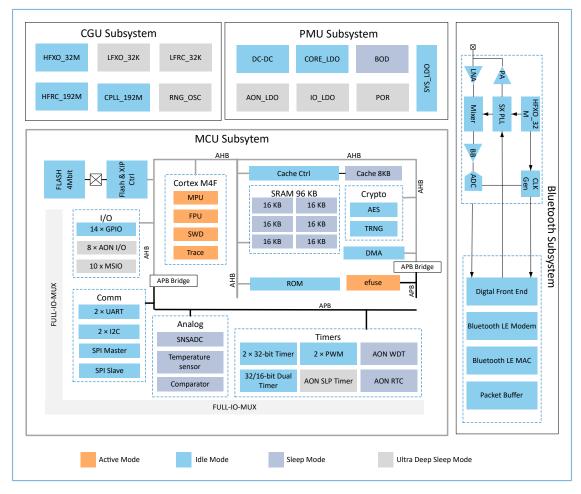

## 1.2 Block Diagram

The SoC block diagram is shown in the figure below.

- Bluetooth subsystem

- A 2.4 GHz transceiver and a digital communication core, both supporting Bluetooth LE 5.3

- MCU subsystem

- ° An Arm<sup>®</sup> Cortex<sup>®</sup>-M4F with all the required memories and peripherals

- Power Management Unit (PMU) subsystem

- Power supply for the whole SoC, including internal modules and external peripherals

- Efficient and reliable SoC power management

- Clock Generation Unit (CGU) subsystem

# GODiX

- Providing stable, low-power, and accurate clock signals

- Optimizing SoC performance and minimizing power consumption, by adjusting clock frequency and selecting an appropriate clock.

## **1.3 Applications**

The device can be used in a rich set of applications.

- IoT applications

- Smart lock and smart home

- Beacon and smart tracker

- Electronic shelf label (ESL)

- Mesh applications

- Asset tracking

- Health and medical applications

- Thermometer

- SpO2 meter

- Blood glucose and pressure meter

- Weight scale

- Bluetooth HID devices

- Remote control

- Gaming controller

- Stylus pen

## 2 Pinout

This chapter describes the pin assignment of the device and provides detailed information for each individual pin.

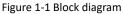

## 2.1 QFN32

The figure below shows the pin assignment for devices in QFN32 package.

Figure 2-1 QFN32 device pinout (top view)

The following table provides the descriptions of pin functionality.

Table 2-1 Pin descriptions

| Pin # | Pin Name | Pin Type         | Description/Default Function                             | Voltage Domain |

|-------|----------|------------------|----------------------------------------------------------|----------------|

| 1     | ХОР      | Analog/RF        | Input of inverting amplifier connected to 32 MHz crystal |                |

| 2     | VDD_RF   | Analog/RF supply | Input of RF supply; connect to VREG.                     |                |

| 3     | VSS_RF   | Analog/RF supply | RF GND; connect to GND.                                  |                |

| 4     | RF_RX    | Analog/RF        | RF transceiver RX input                                  |                |

| 5     | RF_TX    | Analog/RF        | RF transceiver TX output                                 |                |

| 6     | PA_GND   | Analog/RF Supply | RF PA GND; connect to ground.                            |                |

| Pin # | Pin Name    | Pin Type             | Description/Default Function                                                                                                     | Voltage Domain |  |  |

|-------|-------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------|----------------|--|--|

| 7     | VBAT_RF     | Analog/RF Supply     | RF HPA and Bandgap supply; connect to VBATL.                                                                                     |                |  |  |

| 8     | GPIO_0      | Digital I/O          | General-purpose I/O; default: SWD_CLK                                                                                            |                |  |  |

| 9     | GPIO_1      | Digital I/O          | General-purpose I/O; default: SWD_IO                                                                                             | VDDIOO         |  |  |

| 10    | VIO_LDO_OUT | PMU                  | Output of on-chip I/O supply regulator; connect internally to<br>VDDIO0.<br>Typical output voltage: 1.8 V.                       |                |  |  |

| 11    | CHIP_EN     | Analog/PMU           | Master Enable for chip reset pin<br>Minimum value of high level for CHIP_EN: 1 V                                                 |                |  |  |

| 12    | DIGCORE     | Analog/PMU           | On-chip LDO output for digital core                                                                                              |                |  |  |

| 13    | VREG        | Analog/PMU           | DC-DC feedback pin of switch regulator/SYS_LDO output pin                                                                        |                |  |  |

| 14    | VSW         | Analog/PMU           | DC-DC converter switching node                                                                                                   |                |  |  |

| 15    | VBATL       | Analog/PMU           | Power supply: 2.0 V to 3.63 V                                                                                                    |                |  |  |

| 16    | MSIO_7      | PMU/Mixed Signal I/O | Configurable mixed-signal I/O with digital GPIO and SNSADC<br>Multiplexed by writing eFuse using external 2.5 V voltage.         |                |  |  |

| 17    | MSIO_6      | Mixed Signal I/O     |                                                                                                                                  | VBATL          |  |  |

| 18    | MSIO_5      | Mixed Signal I/O     |                                                                                                                                  |                |  |  |

| 19    | MSIO_4      | Mixed Signal I/O     | Configurable mixed-signal I/O with digital GPIO and SNSADC                                                                       |                |  |  |

| 20    | MSIO_3      | Mixed Signal I/O     |                                                                                                                                  |                |  |  |

| 21    | MSIO_9      | Mixed Signal I/O     | Configurable mixed-signal I/O with digital GPIO<br>Multiplexed by RTC_32K_OUT.                                                   |                |  |  |

| 22    | MSIO_8      | Mixed Signal I/O     | Configurable mixed-signal I/O with digital GPIO<br>Multiplexed by RTC_32K_IN.                                                    |                |  |  |

| 23    | AON_GPIO_0  | Digital I/O          |                                                                                                                                  |                |  |  |

| 24    | AON_GPIO_1  | Digital I/O          | Always-on GPIO, can wake up chip from sleep mode                                                                                 |                |  |  |

| 25    | VDDIO_1     | Digital I/O supply   | Digital I/O supply input.<br>Support external 1.8 V–3.6 V input voltage                                                          | VDDIO1         |  |  |

| 26    | AON_GPIO_2  | Digital I/O          |                                                                                                                                  |                |  |  |

| 27    | AON_GPIO_3  | Digital I/O          |                                                                                                                                  |                |  |  |

| 28    | AON_GPIO_4  | Digital I/O          | Always-on GPIO, can wake up chip from sleep mode                                                                                 |                |  |  |

| 29    | AON_GPIO_5  | Digital I/O          |                                                                                                                                  |                |  |  |

| 30    | AON_GPIO_6  | Digital I/O          |                                                                                                                                  |                |  |  |

| 31    | тм          | Analog/RF            | <ul><li>Input pin, used for factory test mode selection</li><li>1: factory test mode.</li><li>0: normal operation mode</li></ul> |                |  |  |

| Pin # | Pin Name | Pin Type  | Description/Default Function                                   | Voltage Domain |

|-------|----------|-----------|----------------------------------------------------------------|----------------|

|       |          |           | Note:                                                          |                |

|       |          |           | In practice, the value is set to 0 by default; connect to GND. |                |

| 32    | XON      | Analog/RF | Output of inverting amplifier connected to 32 MHz crystal      |                |

#### **Note**:

The pad drive strength for all IOs (including GPIO/ AON\_GPIO/ MSIO) can be configured to 2 mA/4 mA/8 mA/12 mA under 3.3 V voltage.

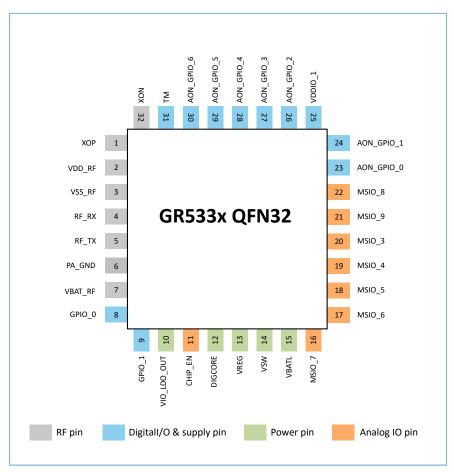

## 2.2 QFN48

The figure below shows the pin assignment for devices in QFN48 package.

Figure 2-2 QFN48 device pinout (top view)

The following table provides the descriptions of pin functionality.

| Pin # | Pin Name           | Pin Type             | Description / Default Function                                                                                          | Voltage Domain |  |  |

|-------|--------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------|----------------|--|--|

| 1     | VDD_RF             | Analog/RF supply     | Input of synthesizer RF supply; connect to VREG.                                                                        |                |  |  |

| 2     | VSS_RF             | Analog/RF supply     | RF GND; connect to GND.                                                                                                 |                |  |  |

| 3     | RF_RX              | Analog/RF            | RF transceiver RX input                                                                                                 |                |  |  |

| 4     | RF_TX              | Analog/RF            | RF transceiver TX output                                                                                                |                |  |  |

| 5     | VBAT_RF            | Analog/RF Supply     | RF HPA and Bandgap supply; connect to VBATL.                                                                            |                |  |  |

| 6     | GPIO_0             | Digital I/O          | General-purpose I/O; default: SWD_CLK                                                                                   |                |  |  |

| 7     | GPIO_1             | Digital I/O          | General-purpose I/O; default: SWD_IO                                                                                    |                |  |  |

| 8     | GPIO_2             | Digital I/O          |                                                                                                                         |                |  |  |

| 9     | GPIO_3             | Digital I/O          |                                                                                                                         |                |  |  |

| 10    | GPIO_4             | Digital I/O          |                                                                                                                         |                |  |  |

| 11    | GPIO_5 Digital I/O |                      | General-purpose I/O                                                                                                     | VDDIO0         |  |  |

| 12    | GPIO_6             | Digital I/O          |                                                                                                                         |                |  |  |

| 13    | GPIO_7             | _7 Digital I/O       |                                                                                                                         |                |  |  |

| 14    | VIO_LDO_OUT        | ΡΜυ                  | Output of on-chip I/O supply regulator; connect internally to<br>VDDIO0.<br>Typical output voltage: 1.8 V.              |                |  |  |

| 15    | CHIP_EN            | Mixed Signal IN      | Master Enable for chip reset pin<br>Minimum value of high level for CHIP_EN: 1 V                                        |                |  |  |

| 16    | DIGCORE            | Analog/PMU           | On-chip LDO output for digital core                                                                                     |                |  |  |

| 17    | VREG               | Analog/PMU           | DC-DC feedback pin of switch regulator/SYS_LDO output pin                                                               |                |  |  |

| 18    | VSW                | Analog/PMU           | DC-DC converter switching node                                                                                          |                |  |  |

| 19    | VSS_BUCK           | PMU                  | DC-DC converter Power GND                                                                                               |                |  |  |

| 20    | VBATL              | PMU                  | Power supply: 2.0 V to 3.63 V                                                                                           |                |  |  |

| 21    | MSIO_7             | PMU/Mixed Signal I/O | Configurable mixed-signal I/O with digital GPIO and SNSADC<br>Multiplexed by writing eFuse using external 2.5 V voltage |                |  |  |

| 22    | MSIO_6             | Mixed Signal I/O     |                                                                                                                         | 7              |  |  |

| 23    | MSIO_5             | Mixed Signal I/O     |                                                                                                                         |                |  |  |

| 24    | MSIO_4             | Mixed Signal I/O     |                                                                                                                         | VBATL          |  |  |

| 25    | MSIO_3             | Mixed Signal I/O     | Configurable mixed-signal I/O with digital GPIO and SNSADC                                                              |                |  |  |

| 26    | MSIO_2             | Mixed Signal I/O     |                                                                                                                         |                |  |  |

| 27    | MSIO_1             | Mixed Signal I/O     |                                                                                                                         |                |  |  |

| 28    | MSIO_0             | Mixed Signal I/O     |                                                                                                                         |                |  |  |

Table 2-2 Pin descriptions

| Pin # | Pin Name   | Pin Type           | Description / Default Function                                | Voltage Domain |

|-------|------------|--------------------|---------------------------------------------------------------|----------------|

| 20    |            | Mixed Signal 1/0   | Configurable mixed-signal I/O with digital GPIO               |                |

| 29    | MSIO_9     | Mixed Signal I/O   | Multiplexed by RTC_32K_OUT.                                   |                |

| 30    | MSIO_8     | Mixed Signal I/O   | Configurable mixed-signal I/O with digital GPIO               |                |

| 50    | 101310_8   | Wiked Signal I/O   | Multiplexed by RTC_32K_IN.                                    |                |

| 31    | AON_GPIO_0 | Digital I/O        | Always-on GPIO, can wake up chip from sleep mode.             |                |

| 32    | AON_GPIO_1 | Digital I/O        | Always-on GPIO, can wake up chip from sleep mode.             |                |

| 33    | VDDIO_1    | Digital I/O supply | Digital I/O supply input                                      |                |

| 33    |            | Digital I/O supply | Support external 1.8 V–3.6 V input voltage.                   |                |

| 34    | AON_GPIO_2 | Digital I/O        |                                                               |                |

| 35    | AON_GPIO_3 | Digital I/O        |                                                               |                |

| 36    | AON_GPIO_4 | Digital I/O        | Always on CDIO, can write up this from close mode             | VDDIO1         |

| 37    | AON_GPIO_5 | Digital I/O        | Always-on GPIO, can wake up chip from sleep mode.             |                |

| 38    | AON_GPIO_6 | Digital I/O        |                                                               |                |

| 39    | AON_GPIO_7 | Digital I/O        |                                                               |                |

| 40    | GPIO_8     | Digital I/O        |                                                               |                |

| 41    | GPIO_9     | Digital I/O        |                                                               |                |

| 42    | GPIO_10    | Digital I/O        |                                                               |                |

| 43    | GPIO_11    | Digital I/O        | General-purpose I/O                                           |                |

| 44    | GPIO_12    | Digital I/O        |                                                               |                |

| 45    | GPIO_13    | Digital I/O        |                                                               |                |

|       |            |                    | Input pin, used for factory test mode selection               |                |

|       |            |                    | 1: factory test mode                                          |                |

| 46    | ТМ         | Analog/RF          | 0: normal operation mode                                      |                |

|       |            |                    | Note:                                                         |                |

|       |            |                    | In practice, the value is set to 0 by default; connect to GND |                |

| 47    | XON        | Analog/RF          | Output of inverting amplifier connected to 32 MHz crystal     |                |

| 47    | ХОР        | Analog/RF          | Input of inverting amplifier connected to 32 MHz crystal      |                |

| +0    | AUF        |                    |                                                               |                |

#### **Note**:

The pad drive strength for all IOs (including GPIO/ AON\_GPIO/ MSIO) can be configured to 2 mA/4 mA/8 mA/12 mA under 3.3 V voltage.

## **2.3 Pin Properties**

## 2.3.1 PMU Pin Properties

| No. | Pin Name    | Input/Output/GND | Min. | Тур. | Max. | Unit |

|-----|-------------|------------------|------|------|------|------|

| 1   | VDD_RF      | Input            | 1    | 1.05 | 1.21 | V    |

| 2   | VSS_RF      | GND              | -    | 0    | -    | V    |

| 3   | VBAT_RF     | Input            | 2.0  | 3.3  | 3.63 | V    |

| 4   | VIO_LDO_OUT | Output           | 1.7  | 1.8  | 3.63 | V    |

| 5   | CHIP_EN     | Input            | 0    | -    | 3.63 | V    |

| 6   | DIGCORE     | Output           | 0.85 | 0.9  | 1.1  | V    |

| 7   | VREG        | Output           | 0.95 | 1.05 | 1.21 | V    |

| 8   | VSW         | Output           | -    | -    | -    | V    |

| 9   | VSS_BUCK    | GND              | -    | 0    | -    | V    |

| 10  | VBATL       | Input            | 2.0  | 3.3  | 3.63 | V    |

| 11  | VDDIO_1     | Input            | 1.7  | 1.8  | 3.63 | V    |

| 12  | тм          | Input            | -    | 0    | -    | V    |

#### Table 2-3 PMU pin properties

## 2.3.2 I/O Pin Properties

| No. | Pin Name | Default Status<br>After POR | Pull-up/Pull-<br>down Enable<br>After POR | Pull-up/Pull-<br>down Selection<br>After POR | Pin Interrupt | Chip Wake-up | Fast Capability |

|-----|----------|-----------------------------|-------------------------------------------|----------------------------------------------|---------------|--------------|-----------------|

| 1   | GPIO_0   | L                           | Y                                         | PD                                           | Υ             | Ν            | Υ               |

| 2   | GPIO_1   | L                           | Y                                         | PD                                           | Y             | Ν            | Y               |

| 3   | GPIO_2   | L                           | Y                                         | PD                                           | Y             | Ν            | Y               |

| 4   | GPIO_3   | L                           | Y                                         | PD                                           | Y             | Ν            | Y               |

| 5   | GPIO_4   | L                           | Y                                         | PD                                           | Y             | N            | Y               |

| 6   | GPIO_5   | L                           | Y                                         | PD                                           | Y             | N            | Y               |

| 7   | GPIO_6   | L                           | Y                                         | PD                                           | Y             | N            | Y               |

| 8   | GPIO_7   | L                           | Y                                         | PD                                           | Y             | N            | Y               |

| 9   | MSIO_7   | Hi-Z                        | N                                         | -                                            | N             | N            | Y               |

| 10  | MSIO_6   | Hi-Z                        | N                                         | -                                            | N             | N            | Y               |

| 11  | MSIO_5   | Hi-Z                        | N                                         | -                                            | N             | N            | Υ               |

| 12  | MSIO_4   | Hi-Z                        | N                                         | -                                            | N             | N            | Υ               |

| 13  | MSIO_3   | Hi-Z                        | N                                         | -                                            | N             | N            | Y               |

| 14  | MSIO_2   | Hi-Z                        | N                                         | -                                            | Ν             | N            | Y               |

#### Table 2-4 I/O pin properties

| No. | Pin Name   | Default Status<br>After POR | Pull-up/Pull-<br>down Enable<br>After POR | Pull-up/Pull-<br>down Selection<br>After POR | Pin Interrupt | Chip Wake-up | Fast Capability |

|-----|------------|-----------------------------|-------------------------------------------|----------------------------------------------|---------------|--------------|-----------------|

| 15  | MSIO_1     | Hi-Z                        | Ν                                         | -                                            | Ν             | Ν            | Y               |

| 16  | MSIO_0     | Hi-Z                        | Ν                                         | -                                            | Ν             | Ν            | Y               |

| 17  | MSIO_9     | Hi-Z                        | N                                         | -                                            | Ν             | Ν            | Y               |

| 18  | MSIO_8     | Hi-Z                        | Ν                                         | -                                            | Ν             | Ν            | Y               |

| 19  | AON_GPIO_0 | L                           | Y                                         | PD                                           | Y             | Y            | Y               |

| 20  | AON_GPIO_1 | L                           | Y                                         | PD                                           | Y             | Y            | Y               |

| 21  | AON_GPIO_2 | L                           | Y                                         | PD                                           | Y             | Y            | Y               |

| 22  | AON_GPIO_3 | L                           | Y                                         | PD                                           | Y             | Y            | Y               |

| 23  | AON_GPIO_4 | L                           | Y                                         | PD                                           | Y             | Y            | Y               |

| 24  | AON_GPIO_5 | L                           | Y                                         | PD                                           | Y             | Y            | Y               |

| 25  | AON_GPIO_6 | L                           | Y                                         | PD                                           | Y             | Y            | Y               |

| 26  | AON_GPIO_7 | L                           | Y                                         | PD                                           | Y             | Y            | Y               |

| 27  | GPIO_8     | L                           | Y                                         | PD                                           | Y             | N            | Y               |

| 28  | GPIO_9     | L                           | Y                                         | PD                                           | Y             | N            | Y               |

| 29  | GPIO_10    | L                           | Y                                         | PD                                           | Y             | N            | Y               |

| 30  | GPIO_11    | L                           | Y                                         | PD                                           | Y             | Ν            | Y               |

| 31  | GPIO_12    | L                           | Y                                         | PD                                           | Y             | N            | Y               |

| 32  | GPIO_13    | L                           | Y                                         | PD                                           | Y             | N            | Y               |

Abbreviations mentioned above are listed in the table below:

Table 2-5 Abbreviations related to pin properties

| Properties                            | Abbreviation | Description                       |

|---------------------------------------|--------------|-----------------------------------|

|                                       | Hi-Z         | High impendence                   |

| Default status after POR              | Н            | High level                        |

|                                       | L            | Low level                         |

| Pull-up/Pull-down enable after POR    | Υ            | Enabled                           |

|                                       | Ν            | Disabled                          |

| Pull-up/Pull-down selection after POR | PU           | Pull-up                           |

| run-up/run-uown selection after rok   | PD           | Pull-down                         |

| Pin interrupt                         | Ν            | No                                |

| Thin include                          | Y            | Yes                               |

| Fast capability                       | Ν            | Fast capability is not supported. |

| Properties | Abbreviation | Description                   |  |

|------------|--------------|-------------------------------|--|

|            | Y            | Fast capability is supported. |  |

## 3 Minimal Design for GR533x SoC

The absolute necessary sections required for the GR533x SoC minimal system operation include

- Power supply

- Clock

- RF

- I/O pins

- SWD interfaces

To ensure the proper operation of a GR533x SoC, the design guidelines for the schematic diagram and the PCB layout are illustrated in the following sections.

## 3.1 Schematic Design Guideline

For the minimal schematic for a GR533x SoC, see "Section 3.4 Reference Design".

## 3.1.1 Power Supply

### 3.1.1.1 Introduction

GR533x SoCs are powered by external power sources through VBATL (voltage range: 2.0 V to 3.63 V).

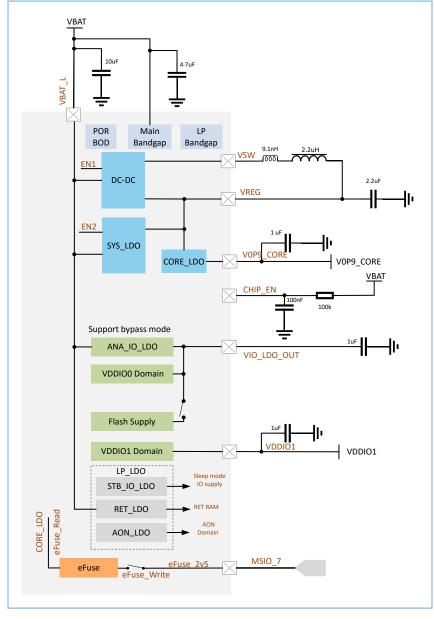

Figure 3-1 Power architecture

As shown in Figure 3-1, the GR533x power supply architecture is based on the PMU that generates the following supplies from an external supply through VBATL.

- DC-DC/SYS\_LDO: supply for RF domain and core LDO (Enabled by default).

- CORE\_LDO: supply for digital logic blocks (Enabled by default).

- AON\_LDO: supply for AON blocks (Enabled by default).

- RET\_LDO: retention supply for memory instances (Enabled by default).

- ANA\_IO\_LDO: Used to generate the I/O voltage to supply the pads of GR533x and the external devices connecting to GR533x. It is also used to supply power to the stacked Flash (Enabled by default).

- STB\_IO\_LDO: Used to replace ANA\_IO\_LDO during sleep, which can help reduce sleep current.

- VDDIO1: supply for I/O1 group; from external power voltage or VIO\_LDO\_OUT.

- **MSIO\_7:** input 2.5 V external voltage to burn eFuse. By burning the eFuse configuration, you can disable the SWD debugging function that is multiplexed by GPIO\_0/GPIO\_1.

Both VBATL and VBAT\_RF come from the battery voltage VBAT. The VBAT\_RF voltage is supplied to the RF domain alone, and the VBATL voltage is the input voltage of all blocks.

**↓**Tip:

- To avoid the switch overshoot caused by battery welding, connect a resistor  $(0.39 \Omega 1 \Omega)$  between the battery and VBATL in series when powering on a GR533x SoC.

- It is recommended to convert the battery voltage to 3.3 V with LDO before supplying VBATL.

#### 3.1.1.2 Power-on Sequence

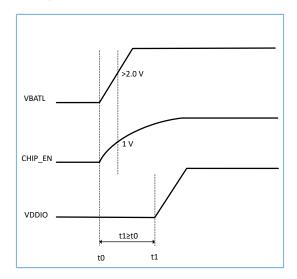

The figure below shows the power-on sequence for GR533x.

#### 🛄 Note:

- After power-on, when CHIP\_EN reaches 1 V, VBATL shall be above 2.0 V.

- Do not power on VDDIO before VBATL.

- When GR533x works as Slave, VBATL cannot be powered on after CHIP\_EN is pulled low. Otherwise, the I/O state might be out of control and forced to output high level.

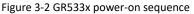

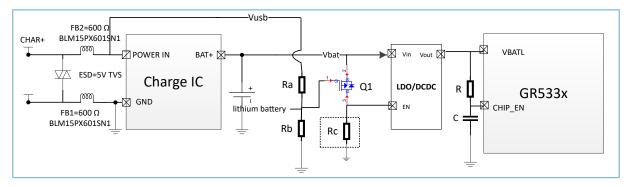

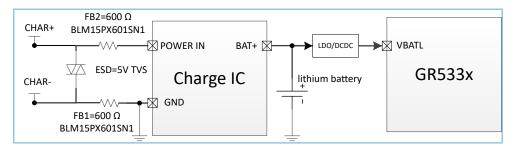

In GR533x applications where devices are supplied by rechargeable batteries but the charger does not support power path management (PPM), when the battery is recharged after its voltage decreases to 0 V (battery depletion due to self-discharge in long-term shipping or storage), the system will fail to be started because it fails to follow the power-on sequence. To avoid this problem, it is recommended to follow the charger solutions below:

#### • Use a charger with PPM instead.

To use a charger that supports system power path management, follow the recommended circuit design in Figure 3-3.

- The battery charging path and the system power supply path can be managed independently: When battery voltage drops to 0 V, connect the charger with an external power source from the USB port. After the input power going through Qbypass and Qrvs, the voltage V<sub>SYS</sub> supplies the system, and the Vbat controlled by Qswitch supplies the 0 V battery.

- When charging starts, V<sub>SYS</sub> will instantly rise to the pre-set value, and GR533x VBATL will also instantly reach the operating voltage or above. The system can keep working normally in this case, thanks to the delay circuit on CHIP\_EN that helps ensure GR533x power-on sequence.

Figure 3-3 Reference design for charger with PPM

- Continue using a charger without PPM.

- In most cases, the battery voltage is converted to the constant voltage 3.3 V through LDO before supplying GR533x. As path management is not supported, use a MOSFET (Q1) to control LDO, and ensure the LDO is only enabled after the preset battery level is reached (sufficient to ensure normal operation of GR533x), so that the system can be started normally.

- During system charging, the gate voltage of Q1 (Vg) is obtained through the voltage divider composed of two resistors (Ra and Rb). When Ra is set to be equal to Rb, Vg is set to 2.5 V, and the condition for turning on Q1 during the charging is: Vbat ≥ 2.5V + |Vgs(th)|, in which Vgs(th) represents the threshold gate-to-source voltage of the MOSFET (Q1).

- Source voltage of Q1 (Vs) equals Vbat, and rises gradually during charging. When Vbat reaches Vgs(th), Q1 is turned on, and the voltage at the EN pin of LDO (V<sub>LDO\_EN</sub>) equals Vbat; at this point, LDO is enabled, and GR533x can be started normally.

During charging, the relations between Q1 state and  $V_{\text{LDO}\_\text{EN}}$  are as follows:

- When Vbat < 2.5 V + |Vgs(th)|, Vgs fails to reach Vgs(th), and therefore Q1 is in cutoff state; V<sub>LDO\_EN</sub> equals 0 V.

- When Vbat ≥ 2.5 V + |Vgs(th)|, Vgs reaches Vgs(th), and therefore Q1 is in conducting state; V<sub>LDO\_EN</sub> equals Vbat.

When the system is working normally without charging, and the USB port is not connected to an external power source, Vg of Q1 is 0 V, determined by the pull-down resistor Rb; Q1 is in conducting state, and  $V_{LDO_{EN}}$  equals Vbat.

#### To obtain Vg: Vg = Vusb x Rb / (Ra + Rb)

Figure 3-4 Reference design for charger not supporting PPM

#### 🛄 Note:

- The MOSFET Q1 is a P-channel MOSFET (PMOS).

- Resistances of Ra and Rb can be set according to the parameters of Q1.

- It is recommended to reserve Rc for setting the initial state of LDO. If Rc is surface-mounted, leakage current I (I = Vbat/Rc) will be generated, and will incur higher system power consumption.

Recommended MOSFETs are detailed in the table below:

| Туре | Part Number | Vgs (th)         | ld (μA) | R <sub>DS(ON)</sub> @ Vgs = -2.5 V | Footprint<br>Reference | Manufacturer        |

|------|-------------|------------------|---------|------------------------------------|------------------------|---------------------|

| PMOS | CJBB3139K   | > -0.35 V (Typ.) | -0.66   | 780 mΩ                             | DFN1006-3L-A           | JSCJ                |

| PMOS | NTK3139P    | > -0.45 V (Typ.) | -1      | 520 mΩ                             | SOT-723                | ON<br>Semiconductor |

Alternatively, you can also add an external circuit that enables path management for the charger, so that GR533x can be started normally.

### 3.1.1.3 I/O LDO

The GR533x has an on-chip linear LDO regulator that supplies always-on blocks, including always-on I/Os and digital logic blocks. Additionally, this regulator can supply external components (sensors) which interface to the GR533x. The LDO is capable of supplying up to 30 mA load current.

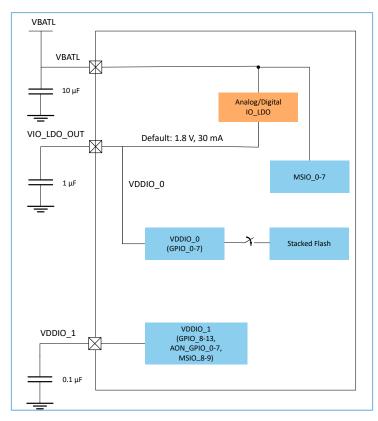

The output of this regulator is the VIO\_LDO\_OUT pin. A 1 µF decoupling capacitor should be connected to this pin. Three I/O voltage domains are provided for GR533x: two digital voltage domains (VDDIO\_0 and VDDIO\_1), as well as one mixed signal I/O domain MSIO, corresponding to reference voltage levels at VDDIO\_0, VDDIO\_1, and VBATL respectively. Figure 3-5 is a circuit diagram showing the connection between VIO\_LDO\_OUT and the I/O domains.

Figure 3-5 Connection between VIO\_LDO\_OUT and I/O domains

#### **Note**:

The voltage domain VDDIO\_1 supplies GPIO\_8–GPIO\_13 and AON\_GPIO\_0 – AON\_GPIO\_7 and MSIO\_8–MSIO\_9; VDDIO\_0 is bonded to VIO\_LDO\_OUT internally and supplies GPIO\_0–GPIO\_7; VDDIO\_0 also supplies GR533x internal Flash through a controllable switch.

#### 3.1.1.4 Power Supply Scheme

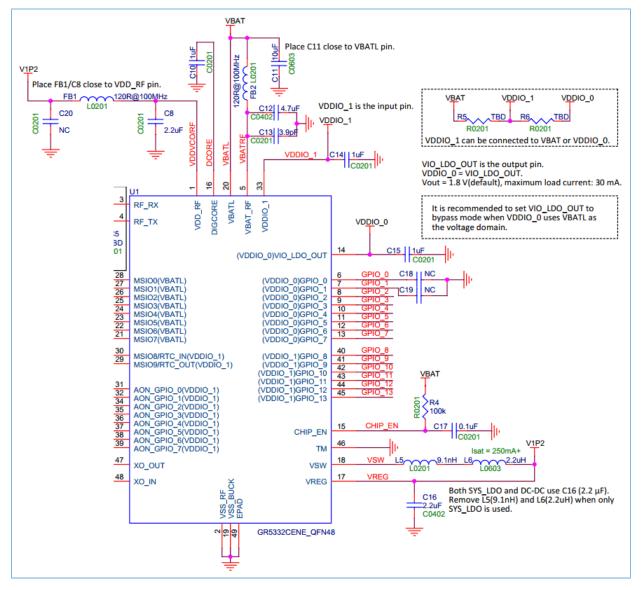

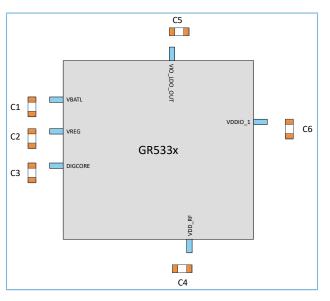

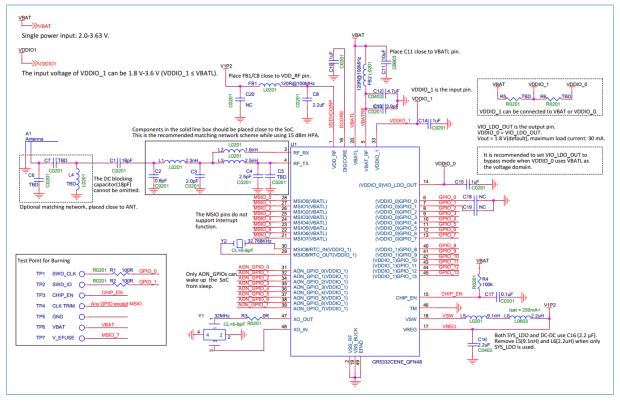

GR533x SoCs are equipped with a complete set of power management modules which guarantee the smooth and secure functioning of the GR533x SoCs. This section introduces the GR533x reference circuit design by taking a GR5332 SoC in QFN48 package as an example (see the figure below).

Figure 3-6 Power section of GR533x

The detailed pin descriptions and connection guidance are as follows:

- VDD\_RF: internal RF block supply, connected to V1P2 (output power net of DC-DC switching regulator) and a 2.2 μF decoupling capacitor.

- DIGCORE: output of digital LDO, which supplies the digital core logic. Connect a 1 μF decoupling capacitor to this pin.

- VBATL: input supply for chip ranging from 2.0 V to 3.63 V; connected to a 10 μF decoupling capacitor; the ripple noise of the power supply does not exceed 40 mV.

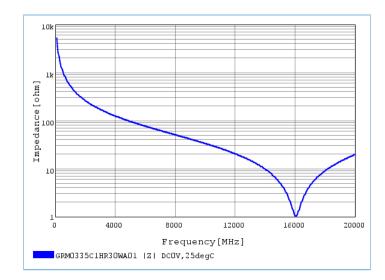

- VBAT\_RF: connected to VBATL, as well as a 4.7 µF decoupling capacitor. Connect a 3.9 pF capacitor in parallel to filter out high-order harmonics. The capacitance of the pF capacitor can be adjusted to meet specific requirements for suppressing harmonics. The material selection is based on ensuring the minimum impedance at the positions where harmonic suppression is needed.

- VIO\_LDO\_OUT: connected to VDDIO0 internally by default, output of the on-chip VDDIO LDO regulator, used to supply the on-chip Flash. It can also supply the VDDIO pins and external sensors with load current up to 30 mA. Connected to a 1 μF decoupling capacitor

- VSW: DC-DC switching regulator output, connected to two inductors in series: a 9.1 nH inductor for reducing RF interference caused by switching noise and a 2.2 μH power inductor, as well as a 2.2 μF capacitor, to supply the SoC from V1P2 as a complete DC-DC circuit. The pin is also connected to VDD\_RF through external circuits

- **VREG:** feedback pin from the DC-DC switching regulator output (mux with SYS\_LDO output), connected to V1P2.

- VDDIO\_1: Provide power for I/O1 voltage domain; supplied from VIO\_LDO\_OUT or an external power source; connected to a 1 μF decoupling capacitor.

#### **Tip**:

- External input voltage to the VIO\_LDO\_OUT pin is prohibited. For example, it is strictly forbidden to directly connect VBATL to the VIO\_LDO\_OUT pin in the external circuit of the SoC. If the CHIPEN pin is pulled low and an external power supply is connected to this pin, it may cause leakage current.

- When the VIO\_LDO\_OUT output voltage is the same as the VBATL voltage, it is recommended to set VIO\_LDO\_OUT to bypass mode by configuring the eFuse.

Recommended capacitors, ferrite beads, and inductors are listed in Table 3-2, Table 3-3, and Table 3-4.

| Reference     | Description                                             | Value    | Package | Mfg Part #        |

|---------------|---------------------------------------------------------|----------|---------|-------------------|

| C8            | CAP, CER, 2.2 uF, 10%, X5R, 0201, 6.3 V,<br>2.2 μF 0201 |          | 0201    | Murata            |

|               | -55°C to +85°C                                          |          |         | GRM033R60J225ME01 |

| C16           | CAP, CER, 2.2 uF, 10%, X6S, 0402, 10 V,                 | 2.2 μF   | 0402    | Murata            |

|               | -55°C to +105°C                                         | <b>F</b> |         | GRM155C81A225KE11 |

| С9            | CAP, CER, 15 pF (±5%), NPO, 50 V,                       | 15 pF    | 0201    | Murata            |

| 65            | -55°C to +125°C                                         | 19 01    | 0201    | GRM0335C1H150JA01 |

| C10, C14, C15 | CAP, CER, 1 μF (±20%), X6S, 10 V,                       | 1μF      | 0201    | Murata            |

| 010, 014, 015 | -55°C to +105°C                                         | τμı      | 0201    | GRM033C81A105ME05 |

| C11           | CAP, CER, 10 μF (±20%), X6S, 10 V,                      | 10 µF    | 0603    | Murata            |

| C11           | -55°C to +105°C                                         | 10 μι    | 0005    | GRM188C81A106MA73 |

| C12           | CAP, CER, 4.7 μF (±20%), X6S, 10 V,                     | 4.7 μF   | 0402    | Murata            |

| 012           | -55°C to +105°C                                         | τ.7 μι   | 0402    | GRM155C81A475ME01 |

| C13           | CAP, CER, 3.9 pF, +/-0.1 pF, NPO, 0201,                 | 3.9 pF   | 0201    | Murata            |

| 015           | 50V, -55°C to +125°C                                    | 2.2 bi   | 0201    | GJM0335C1H3R9BB01 |

| C17           | CAP, CER, 0.1 μF (±20%), X6S, 10 V,                     | 0.1 μF   | 0201    | Murata            |

| (1)           | -55°C to +105°C                                         | 0.1 μι   | 0201    | GRM033C81C104ME14 |

Table 3-2 Recommended decoupling capacitors and ferrite beads for the power section

| Reference | Description                       | Value            | Package | Mfg Part #    |

|-----------|-----------------------------------|------------------|---------|---------------|

| ED1 ED3   | Ferrite beads, 120 ohm @ 100 MHz, | 120 Ω @ 100 MHz  | 0201    | Murata        |

| FB1, FB2  | 200 mA, 500 mohm                  | 120 12 @ 100 MHZ | 0201    | BLM03AG121SN1 |

#### Table 3-3 Recommended DC-DC inductors (9.1 nH)

| Reference | Value   | DC Resistance (Max) | Saturation Current | Size L x W x H (mm) | Mfg Part #    |

|-----------|---------|---------------------|--------------------|---------------------|---------------|

| L5        | 9.1 nH  | 0.4 Ω               | 250 mA             | 0.6 x 0.3 x 0.3     | Murata        |

|           | 5.1 111 | U-T 12              | 250 1117           |                     | LQP03TN9N1J02 |

#### Table 3-4 Recommended DC-DC inductors (2.2 µH)

| Reference       | Value        | DC Resistance (Typ) | Saturation Current | Size L x W x H (mm) | Mfg Part #               |

|-----------------|--------------|---------------------|--------------------|---------------------|--------------------------|

| L6 2.2 μH ± 20% |              | 0.2 Ω 250 mA        |                    | 1.6 x 0.8 x 0.8     | Murata<br>LQM18PN2R2MGH  |

|                 | 2.2 μH ± 20% | 0.3 Ω               | 250 mA             | 1.6 x 0.8 x 0.8     | Sunlord<br>MPH160809S2R2 |

|                 |              |                     | 0.38 Ω             | 300 mA              | 1.6 x 0.8 x 0.8          |

#### **Tip**:

- The 2.2 µH DC-DC inductors are adopted in DC-DC buck converter circuits in Pulse Skip Mode (PSM) and play a crucial role in these circuits. The saturation current of the circuit, which is the current value at which the nominal inductance decreases by 30%, should be equal to or higher than 250 mA. To ensure secure operation and to improve the performance of GR533x, inductors with higher saturation current and lower direct current resistance are preferred, because a higher direct current resistance means higher power consumption.

- If the system is powered by SYS\_LDO, the 9.1 nH inductor and the 2.2 μH inductor can be removed from the power supply scheme.

## 3.1.2 Clock

### 3.1.2.1 Introduction

GR533x clock source is generated by an external 32 MHz crystal oscillator, and the real-time clock by an external 32.768 kHz crystal oscillator.

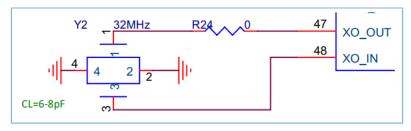

### 3.1.2.2 HFXO\_32M

The system clock, or CPU clock, is provided by an external 32 MHz crystal oscillator which connects to the XO\_IN and XO\_OUT pins of GR533x SoC.

Figure 3-7 External 32 MHz crystal oscillator connection

Table 3-5 shows the specifications for the 32 MHz crystals that can be used for applications, and Table 3-6 shows several recommended crystal candidates.

| Table 3-5 32 MHz crystal specifi | cations |

|----------------------------------|---------|

|----------------------------------|---------|

| Parameter        | Description                                              | Min. | Тур. | Max. | Unit |

|------------------|----------------------------------------------------------|------|------|------|------|

| Crystal Freq     | Crystal oscillator frequency                             | -    | 32   | -    | MHz  |

| ESR              | Equivalent series resistance                             | -    | -    | 100  | Ohm  |

| Cload            | Load capacitance                                         | 6    | -    | 8    | pF   |

| f-Xtal           | Crystal frequency initial tolerance                      | -    | -    | ±50  | ppm  |

| f-Xtal           | Crystal frequency tolerance – over temperature           | -    | -    | ±30  | ppm  |

| f-Xtal           | Crystal frequency tolerance – aging over life of product | -    | -    | ±10  | ppm  |

| P <sub>DRV</sub> | Maximum drive power                                      | -    | -    | 100  | μW   |

#### Table 3-6 Recommended 32 MHz crystals

| Part Number          | ABRACON<br>ABM11W-32MHz-6-R50-J2X | Murata<br>XRCGB32M000F1SBAR0 | Murata<br>XRCGB32M000F1SAAR0 | TXC 8Z32000004   |

|----------------------|-----------------------------------|------------------------------|------------------------------|------------------|

| Frequency            | 32 MHz                            | 32 MHz                       | 32 MHz                       | 32 MHz           |

| Initial tolerance    | ±20 ppm                           | ±10 ppm                      | ±10 ppm                      | ±10 ppm          |

| Tolerance over Temp. | ±20 ppm                           | ±20 ppm                      | ±15 ppm                      | ±20 ppm          |

| Load capacitance     | 6 pF                              | 6 pF                         | 6 pF                         | 8 pF             |

| ESR                  | ≤ 50 Ω                            | ≤ 50 Ω                       | ≤ 50 Ω                       | ≤ 60 Ω           |

| Temperature range    | –40°C to +105°C                   | –40°C to +105°C              | –40°C to +85°C               | –40°C to +85°C   |

| Size (L x W x H, mm) | 2.0 x 1.6 x 0.5                   | 2.0 x 1.6 x 0.65             | 2.0 x 1.6 x 0.65             | 2.5 x 2.0 x 0.55 |

#### 🛄 Note:

- To ensure system stability and XO accuracy, load capacitance of the 32 MHz crystal oscillator should be within the range from 6 pF to 8 pF.

- The 32 MHz crystal oscillator does not require external load capacitors, but it needs to use the mass production tool for frequency offset calibration.

- When designing an application circuit, it is necessary to reserve interfaces or test points for the mass production tool. These include the required SWDCLK, SWDIO, CLK\_TRIM (any GPIOs except MSIOs), GND, VBAT, and the optional MSIO\_7.

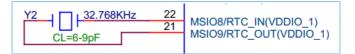

## 3.1.2.3 LFXO\_32K

The GR533x uses a low-power, low-frequency clock in sleep modes, which also extends battery lifespan. The utilization of the external 32.768 kHz crystal oscillator provides better accuracy, resulting in lower overall power consumption.

#### 🛄 Note:

For applications that require less accurate real-time clocks, use an internal LFRC\_32K instead of an external 32.768 kHz crystal oscillator to save device cost.

The GR533x integrates an adjustable load capacitance, so that the external 32.768 kHz crystal oscillator can be directly connected to the RTC\_IN and RTC\_OUT pins of GR533x, and no external load capacitors are required.

Figure 3-8 External 32.768 kHz crystal oscillator connection

The external crystal must meet the recommended operating conditions as indicated in Table 3-7, and Table 3-8 shows examples of crystals that meet the specifications.

| Parameter         | Description                                              | Conditions | Min. | Тур.   | Max.    | Unit |

|-------------------|----------------------------------------------------------|------------|------|--------|---------|------|

| Crystal Freq      | Crystal oscillator frequency                             | -          | -    | 32.768 |         | kHz  |

| ESR               | Equivalent series resistance                             | -          | -    | -      | 100,000 | Ohm  |

| C <sub>load</sub> | Load capacitance                                         | -          | 6    | -      | 9       | pF   |

| f-Xtal            | Crystal frequency initial tolerance                      | -          | -    | -      | ±50     | ppm  |

| f-Xtal            | Crystal frequency tolerance – over temperature and aging | -          | -    | -      | ±250    | ppm  |

| P <sub>DRV</sub>  | Max drive power                                          | -          | -    | -      | 0.5     | μW   |

#### Table 3-8 32.768 kHz crystal oscillator example specifications

| Part Number ABRACON ABS05-32. | 768KHZ-9-T |

|-------------------------------|------------|

|-------------------------------|------------|

| Frequency            | 32.768 kHz       |

|----------------------|------------------|

| Initial tolerance    | ±20 ppm          |

| Tolerance over Temp. | ±250 ppm         |

| Load capacitance     | 9 pF             |

| ESR                  | 90,000 ohms      |

| Temperature range    | -40°C to +85°C   |

| Size (L x W x H, mm) | 1.6 x 1.0 x 0.50 |

#### **Note**:

To ensure system stability and XO accuracy, load capacitance of the 32.768 kHz crystal oscillator should be within the range from 6 pF to 9 pF.

### 3.1.3 RF

#### 3.1.3.1 Introduction

GR533x integrates a 2.4G RF transceiver, which operates based on the mechanisms described below:

- On the receiver side:

- After the antenna receives an RF signal, the receiver digitizes the signal in a path: Low noise amplifier (LNA)

> Mixer > Baseband (BB) amplifier > an analog-to-digital converter (ADC).

- 2. The digitized signals are sent to the digital frontend (DFE) for demodulation.

- 3. The digital frontend provides Automatic Gain Control (AGC) feedback signals to adjust the gain of the LNA and BB amplifier to maximize the signal-to-noise ratio (SNR) at the demodulation.

- On the transmitter side:

- 1. The digital signal from the DFE is transmitted to a phase-locked loop (SXPLL) for modulation.

- 2. The modulated carrier is delivered to a power amplifier (PA) with amplification factor configurable by the digital gain settings.

- 3. The modulated carrier is transmitted to the antenna through a low-power or high-power PA path. The antenna radiates the amplified carrier through electromagnetic waves.

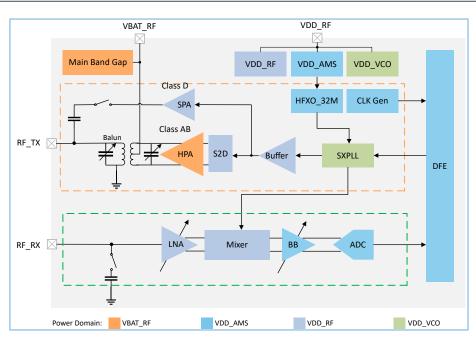

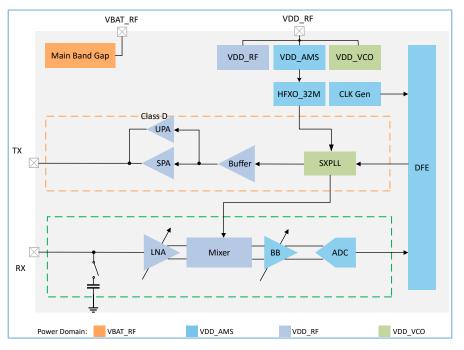

GR5332 differs from GR5331 in the transceiver in use. The block diagrams of the two types of transceivers are presented in Figure 3-9 and Figure 3-10.

Figure 3-9 GR5332 transceiver block diagram

#### **Note**:

- Choose a high-power amplifier (HPA) or a small-power amplifier (SPA) for GR5332 based on the transmission power needed. An HPA supports transmission power between -10 dBm and 15 dBm, whereas -20 dBm and 5 dBm is supported for an SPA.

- The reference clock of SX PLL is generated by HFXO\_32M.

Figure 3-10 GR5331 transceiver block diagram

### 🛄 Note:

- Choose a small-power amplifier (SPA) or an ultra-low power amplifier (UPA) for GR5331/GR5530 based on the transmission power needed. An SPA supports transmission power between -20 dBm and 6 dBm, whereas -15 dBm and 2 dBm is supported for a UPA.

- The reference clock of SX PLL is generated by HFXO\_32M.

For detailed information about RF PA selection and matching circuit for GR533x, see GR533x RF PA Application Note.

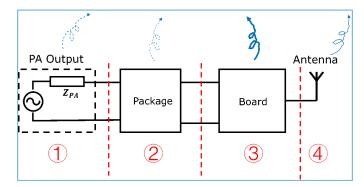

### 3.1.3.2 RF Scheme

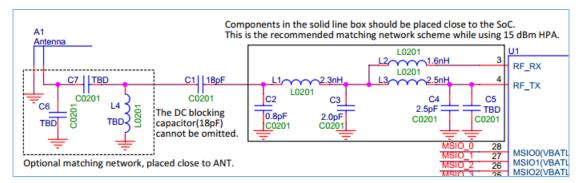

The following figure is the recommended RF matching circuit in the GR533x SoC minimal system.

Two matching networks are recommended for the RF TRX path from the RF\_TX/RX pin to the antenna, to achieve the matching of PA output impedance to antenna impedance.

• Antenna matching network

In the circuit, the left PI matching network (composed the inductor L4 plus capacitors C6 and C7) matches the antenna. Values of the matching component are adjusted according to the actual antenna used. It is recommended to use mature antenna schemes and recommended values from antenna manufacturers.

• SoC matching network

The PI type matching network (composed of the inductors L1, L2, and L3 plus capacitors C2, C3, C4, and C5) on the right matches the PA output impedance of GR533x.

#### 🛄 Note:

• For GR5332 SoCs, C5 is reserved for tuning, and thus is not connected by default.

For GR5331 SoCs, C5 (0.3 pF) is used to suppress seventh-order harmonics.

The DC blocking capacitor (C1) that connects the two matching networks cannot be omitted.

Taking GR5332CENE (in QFN48) as an example, the recommended capacitors and inductors are specified in Table 3-9.

| Reference | Description                                                                       | Value  | Package Size | Mfg Part #               |

|-----------|-----------------------------------------------------------------------------------|--------|--------------|--------------------------|

| C1        | CAP, CER, 18 pF (±5%), NPO, 50 V, -55°C to +125°C                                 | 18 pF  | 0201         | Murata GRM0335C1H180JA01 |

| C2        | CAP, CER, 0.8 pF (±0.1 pF), NPO, 50 V, -55°C to +125°C                            | 0.8 pF | 0201         | Murata GRM0335C1HR80WA01 |

| С3        | CAP, CER, 2.0 pF (±0.1 pF), NPO, 50 V, -55°C to +125°C                            | 2.0 pF | 0201         | Murata GRM0335C1H2R0BA01 |

| C4        | CAP, CER, 2.5 pF (±0.1 pF), NPO, 50 V, -55°C to +125°C                            | 2.5 pF | 0201         | Murata GRM0335C1H2R5BA01 |

| L1        | Inductor, CHIP, 2.3 nH (±0.1 nH), 200 mohm, Q = 14 @<br>250 MHz, -55°C to +125°C, | 2.3 nH | 0201         | Murata LQP03TN2N3B02     |

| L2        | Inductor, CHIP, 1.6 nH (±0.1 nH), 150 mohm, Q = 14 @<br>250 MHz, -55°C to +125°C  | 1.6 nH | 0201         | Murata LQP03TN1N6B02     |

| L3        | Inductor, CHIP, 2.5 nH (±0.1 nH), 200 mohm, Q = 14 @<br>250 MHz, -55°C to +125°C, | 2.5 nH | 0201         | Murata LQP03TN2N5B02     |

#### Table 3-9 Recommended components for the RF section

#### 🛄 Note:

For details about the RF matching components specific to a GR533x part number, see the corresponding BOM table.

## 3.1.4 I/O Pins

The GR533x has software-configurable I/O pin assignment where different peripherals can be multiplexed out on different chip pins. When configured to GPIOs, they can be set as input, output, with configurable pull-up or pull-down resistors. I/O pins retain their last state when system enters the sleep or ultra deep sleep mode. Only AON\_GPIOs can be used to wake up the system from sleep modes.

#### 🛄 Note:

- All I/Os can retain their output levels when the system enters sleep mode. During sleep mode, if an I/O is set to input mode, the external level should either be a specified high level (where the external voltage equals the corresponding I/O power domain voltage) or a low level (0 V). Any other voltage may cause leakage current and result in excessive power consumption in sleep mode.

- MSIO\_0–MSIO\_9 are in high impedance state by default.

- Except MSIO\_0–MSIO\_9, the I/O default state is input mode with pull-down.

- All I/Os (except MSIO\_0–MSIO\_9) can be configured as being triggered by high level, low level, rising edge, falling edge, or both edges.

- All I/Os support four configurable output drive strengths and two slew rate options: The fast slew rate should be used when speed or timing is a concern; the slow slew rate is used to reduce the switching noise.

- All I/Os can be individually multiplexed to all peripherals for layout flexibility.

- Input voltages of all I/Os and VIO\_LDO\_OUT/VDDIO\_1 should not be higher than the VBATL voltage.

## 3.1.5 SWD Interfaces

GR533x connects to J-Link for debugging by using Serial Wire Debug (SWD) interfaces. The following table shows the pins to which the SWD interfaces connect in QFN48 and QFN32 packages.

| SWD     | Pin # (QFN48) | Pin # (QFN32) |

|---------|---------------|---------------|

| SWD_CLK | Pin 6         | Pin 8         |

| SWD_IO  | Pin 7         | Pin 9         |

#### 🛄 Note:

- These pins can be multiplexed as GPIOs when the SWD interfaces are not in use.

- The SWD debugging function can be disabled by burning the eFuse configuration.

## 3.2 PCB Design and Layout Guideline

### 3.2.1 PCB Layer Stackup

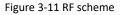

A 4-layer PCB layout is recommended to be used for all GR533x package options. Figure 3-12 shows the recommended layer stackup (thickness: 1.6 mm) of GR533x.

Figure 3-12 GR533x PCB layer stackup

- L1: top layer where components, RF transmission lines, and key signal lines are placed

- L2: internal ground plane, used for both the ground return path and the reference plane for the 50 ohm RF transmission line

- L3: internal routing layer, used to split power domains and place a small number of signal lines

• L4: bottom layer where the integrity of a ground plane should be maintained

## 3.2.2 Components Layout

All components operating at high frequency should have their layout made as compact as possible. This will prevent the cross-coupling between lines and also minimize the parasitic effects which will have a negative impact on the operating parameters.

When designing the layout, make sure the GR533x SoC is placed as close to the antenna interface as possible, and no other traces or components are under the RF routing if possible (the layout and routing of RF components are of higher priority).

## 3.2.3 Power Supply

Power supply is essential to ensure proper operation of an SoC, and therefore special attention should be paid on the layout and routing of the key power systems, which are DC-DC switching regulator and RF input power supply. To avoid system-level issues (such as poor performance in ESD protection and radiation off limits) caused by improper power design, abide by the design hints described in the two following sections.

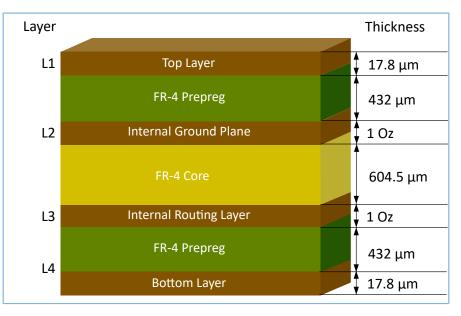

#### 3.2.3.1 DC-DC Switching Regulator

The chip includes a DC-DC switching regulator. To design the PCB layout involving a DC-DC switching regulator,

- Components (L3: 9.1 nH inductor, L4: 2.2 μH inductor, and C15: 2.2 μF capacitor) connected to DC-DC switching regulator should be placed as close to the VSW and VREG pins of the chip as possible. A distance within 3 mm is recommended.

- 2. The net of VSW radiates stronger interference before VSW signals passing through the inductors, and thus should be placed at a minimum distance of 0.2 mm from other power nets and signals, especially V1P2 and DIGCORE.

- 3. C16 should be placed behind L4. The power trace of VREG should go through the DC-DC output capacitor (C16) first before being connected to VREG.

- 4. GND pin of C16 should be placed as close to VSS\_BUCK of the chip as possible. Vias of C16 GND pin should be placed as close to the GND pin as possible. It is recommended to connect the C16 GND pin to VSS\_BUCK by using GND polygon plane, so that the return path of the power can be kept minimal.

- 5. For GR533x in QFN48 package, it is recommended to connect the VSS\_BUCK pin to the EPAD through vias. Avoid connecting them on the same layer.

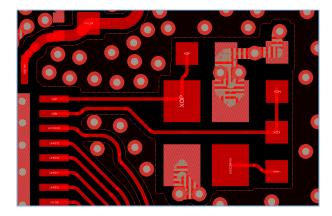

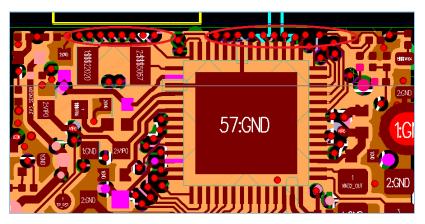

Figure 3-13 Reference layout and routing for DC-DC switching regulator

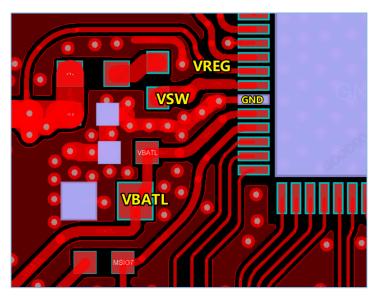

#### 3.2.3.2 RF Input Power Supply

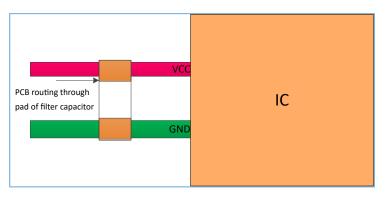

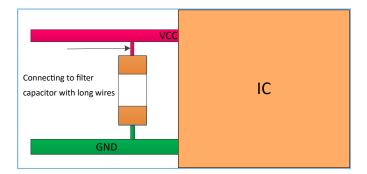

Make sure the following instructions are met when designing RF input power supply in PCB layout, to ensure optimal performance and to avoid excessively high radiation.

- 1. Decoupling capacitors connected to VDD\_VCO and VBAT\_RF should be as close to the corresponding pin as possible (around 1 mm is recommended, and should not exceed 3 mm). Place the capacitors on the same layer with the chip if possible, and make sure the routed trace goes through the capacitors first and then connected to the chip power pins. In case the capacitors are not placed on the same layer with the chip, they can be connected through vias, and the vias should be located close to the decoupling capacitors.

- 2. The power trace should be as short as possible, and at least 0.2 mm wide. A minimum distance at 0.2 mm from other signals should be guaranteed.

- 3. It is recommended to route the V1P2 network directly through the area on the routing layer that is projected by E-PAD (GND) on the bottom of the SoC. If the SoC is placed on Layer 1: For a double-layer PCB layout design, V1P2 network routing shall pass through the E-PAD projection area on Layer 2; for a four-layer PCB layout design, V1P2 network routing shall pass through the E-PAD projection area on Layer 3, as shown below. Moreover, please be cautious not to route the trace too close to the GND plane near the RF pins.

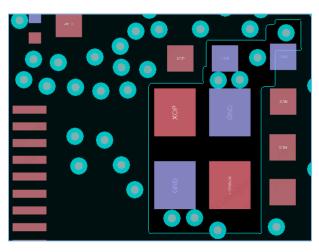

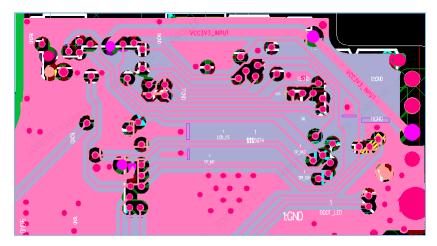

Figure 3-14 Reference layout and routing for RF input power supply

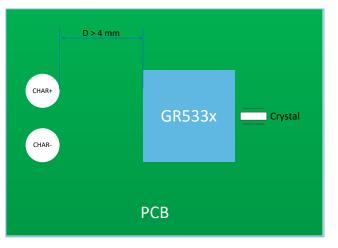

#### 3.2.4 Clock

Place the crystal as close as possible to the corresponding pin of the chip (recommended distance: ≤4 mm). This will minimize any additional capacitive load on the input pins and reduce the chance of crosstalk and interference with other signals on the board. Make sure there is no other trace routed next to/under the crystal or the crystal routing traces, and shield the routing traces of the 32 MHz crystal with GND traces.

By taking 4-layer PCB as an example, if the ground below the crystal is clean and no crosstalk or interference is involved, provide openings underneath the crystal pads (as shown in Figure 3-16) to reduce parasitic capacitance.

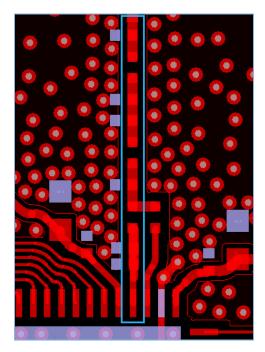

Figure 3-15 Reference clock layout for 4-layer PCB in QFN48

Figure 3-16 Openings under XO pads on 4-layer PCB

### 3.2.5 RF Port

A copper trace with a characteristic impedance of 50  $\Omega$  is required to interconnect the RF port and the antenna. Because the impedance of RF port is not 50  $\Omega$ , a matching network is required to match the port impedance between the RF port and the 50  $\Omega$  transmission line.

Components in this matching network should be placed as close to the RF pins (RF\_RX and RF\_TX) as possible. Try to place the first component no further than 1 mm from the RF pin. Figure 3-17shows the PCB layout of the RF port.

Figure 3-17 RF port PCB layout

# G@DiX

#### 🛄 Note:

- The RF routing traces should be straight and as short as possible. If a curving trace is necessary for a specific structure, an inverted arc is required for a turning, and angles at or less than 90° are not allowed.

- RF routing at the PCB surface (the top layer or the bottom layer) helps avoid using vias or switching layers, and is therefore preferred. Stub routing should be avoided.

Taking the 4-layer PCB layout design as an example, the transmission line is routed as a microstrip using layer-2 ground as the reference plane. The dimensions are:

- Trace width: 559 μm

- Spacing from trace to top layer: 178 μm

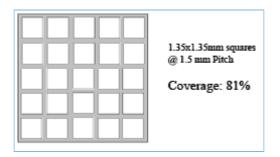

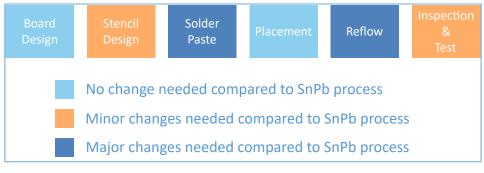

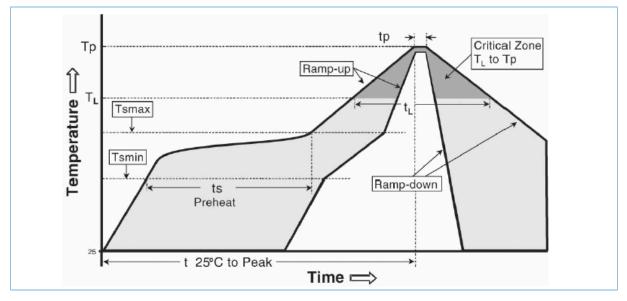

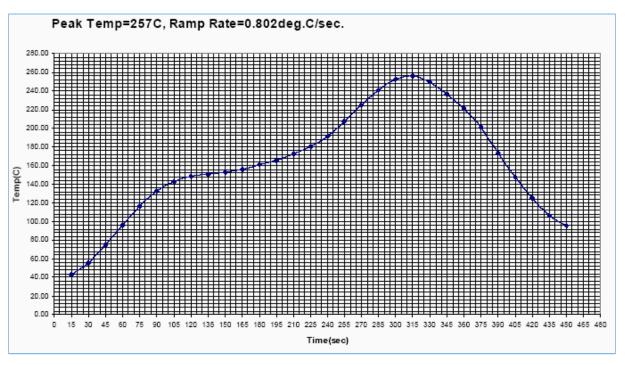

- Spacing from top layer to layer 2: 432 μm